振荡器、触发器、锁存器

在很多涉及到电子电路的文章中我们都能看到「振荡器」这个东西,以前经常听到,但从未了解过,总把它想象成一个可以震动的电子器件,实际上他确实是可以震动的,只是通过这个震动来输出具有周期性的信号,它产生的信号又叫时钟信号。

振荡器

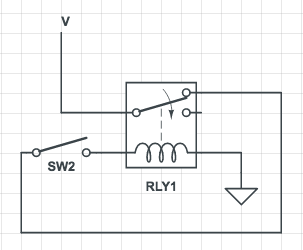

假设有以下电路:

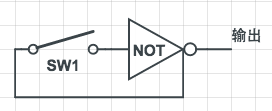

当SW2闭合时,整个电路连通,继电器产生磁力将上面的开关吸下来,导致电路断开,上面的开关又恢复原先的连接状态,电路又连通,又导致开关被吸下来,如此周而复始。只要SW2闭合,整个电路始终保持「通-断-通-断」的状态,该电路可简化为以下形式:

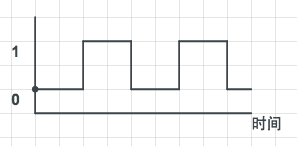

图中的 NOT 是一个反向器,当输入为0时输出1,输入为1时输出0。当 SW1 闭合,NOT 输入为1,输出为0,导致 NOT 的输入又为0,输出为1,如此周而复始。这样的一个电路就称为「振荡器」,我们可以使用下面的图形来描述它的输出:

每个振荡器都有其不同的周期时间,通常我们使用周期的倒数:「频率」来描述它。例如一个振荡器完成一个周期需要0.01s,那么它的频率就是1 / 0.01 = 100Hz,表示它每秒可以变化100次。

触发器

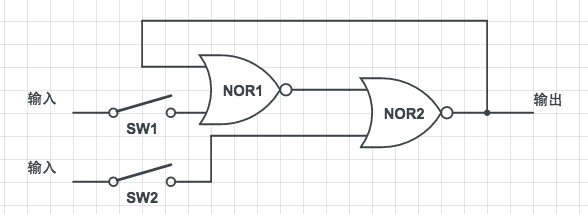

首先来看下面的电路:

在电路中有两个「或非门」,或非门的真值表如下:

| NOR | 0 | 1 |

|---|---|---|

| 0 | 1 | 0 |

| 1 | 0 | 0 |

它的特点是当两端都没有输入时才产生输出。在上面的电路中,NOR1的输出作为 NOR2的输入,NOR2的输出作为 NOR1的输入,这种连接方式称为反馈。这种连接方式也造成了下面的奇特现象:

- 在默认状态下,SW1,SW2均处于断开状态,NOR1的两个输入均为0,所以其输出为1,NOR2的一个输入为0,一个输入为1,所以 NOR2的输出为0,这个0又作为 NOR1的一个输入,如此便保持了一个稳态,电路整体输出0。

- 将 SW1连接,NOR1输出0,NOR2输入1,电路整体输出1。但如果你将 SW1再断开,电路整体仍然输入1,这是因为在你上次连接 SW1时,NOR2输出1,此时 NOR1中上面的输入已经为1了,不管下面的输入是0还是1,NOR1仍保持输出0,所以电路又保持了一个稳态。此时电路始终保持输出1,SW1是否连接对整体无影响。

- 将 SW2连接,NOR2输出0,SW1处于断开状态,NOR1输出1,此时电路整体输出为0并保持稳定。如果再将 SW2断开,此时电路整体仍保持输出为0,因为在上一次连接 SW2后,NOR2输出0,导致 NOR1输出1,此时 NOR2中上面的输入为1,不管下面输入是几,NOR2都输出0,这时SW2是否连接对整体电路无影响。

来总结一下上面的情况:

- 接通 SW1,整体输出1,再断开 SW1对整体输出无影响。

- 接通 SW2,整体输出0,再断开 SW2对整体输出无影响。

它的特点是当 SW1于 SW2处于同样的状态时,有时输出0,有时输出1。当输出改变后,造成这次改变的开关的状态便不再影响输出,只有当另一个开关状态改变时,输出才会改变。这种电路结构统称为「触发器」,他可以用来「记住某些信息」,例如上面的电路中,如果整体输出1,则说明上次连接的开关是 SW1,如果整体输出为0,则说明上次连接的开关是 SW2。

触发器有很多种,上面是最简单的一种叫做「RS 触发器」,使用下面的电路图表示:

(图片来源于 wikipedia)

(图片来源于 wikipedia)

假设我们使用 Q 表示电路的输出状态,Q反 是对 Q 的取反,S 用来置位(把 Q 设为1),R 用来复位(把 Q 设为为0)。当 S 为1时,Q 为1,Q反 为0,当 R 为1时,Q 为0,Q反 为1,当 S,R 均为0时,Q、Q反保持上次的状态不变。把它总结为真值表为:

| 输入 | 输入 | 输出 | 输出 |

|---|---|---|---|

| S | R | Q | Q反 |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 0 | Q | Q反 |

| 1 | 1 | 无意义 | 无意义 |

上面最后一行的两个无意义是因为当 S,R 均为1时,Q 与 Q反 均为0,这与Q、Q反互反相冲突。

D 型触发器

RS 触发器太简单了,而且输入有点麻烦,我们将对电路进行改造使其满足下面的特性:

移除S,R,取而代之的是一个数据输入端和一个保持位。数据输入端输入0或1,保持位用来保持住电路的整体输出,当它为1时,电路整体输出随数据输入端的改变而改变,当它为0时,数据输入端的改变不影响电路整体输出,也就是说电路「记住了」上一次保持位为1时的输出。

那么该如何改造呢?观察 RS 触发器的真值表,可以发现当 S,R 的值互反时,Q, Q反与S,R 保持相同的值,此时电路整体输出随输入的改变而改变,这对应着保持位为1时的状态。当S,R 值均为0时,Q, Q反与上一次的状态相同,这对应着保持位为0时的状态。

我们的目标之一是有一个保持位的信号,它能控制电路输出是否保持上一次的状态,也就是说保持位要能做到:

- 可以把S,R 同时强制设为0,此时保持位为0

- 不影响 S,R 的值,此时保持位为1

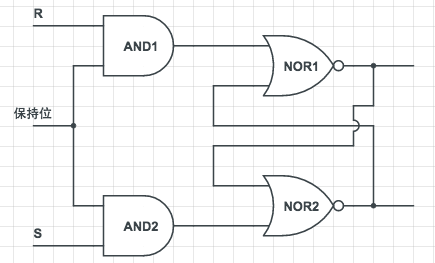

结合着RS 触发器的真值表看,答案已经很明显了,就是使用「与门」。下面对电路进行第一步改造:

当保持位为1时,R,S 分别与其同时作为与门的输入,此时保持位并不影响R,S 通过与门后的结果。当保持位为0时,不论 R,S 输入为几,与门总是输出0,此时可以说保持位把R,S 强行设为了0。

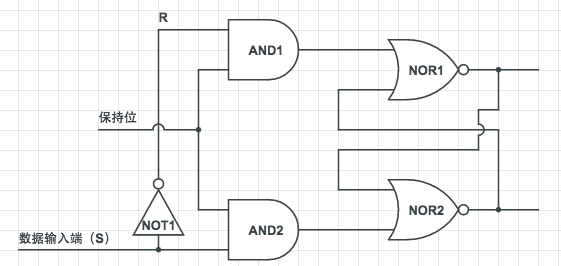

现在保持位的功能已经实现了,但是整体还有两个输入端 R,S。我们发现在 R,S 的4种输入情况中,只有前三种是有意义的,而第三行同时为0的情况已经可以被保持位实现了,也就是说 R,S 其实只有两种状态,且应该处于一种互反的情况,所以可以用一个非门来解决:

现在 S,R已经处于互反状态了,整体电路的数据输入端只有一个 S。现在的触发器结构已经满足前面的要求了,而这种触发器也称为「D 型触发器」。

D 型锁存器

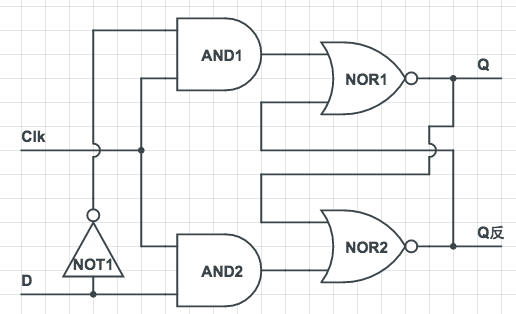

通常情况下,D 型触发器的保持位由「时钟信号」控制,也就是前面的「振荡器」所发出的具有周期性的时钟信号。

D 是唯一的一个数据输入端,此时这个电路就是「D 型锁存器」。它的功能与上面的 D 型触发器基本相同,只是保持位由一个时钟信号代替,由时钟来控制什么时候保持数据。这时突然感觉到汉语的博大精深与老一辈科研人员的智慧,这个电路名叫「锁存器」,而电路的功能可不就是又锁又存么,非常的形象。

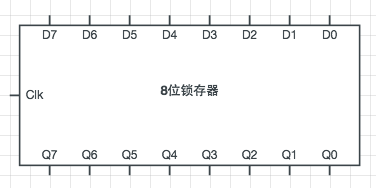

上面的锁存器只能保存一位的数据,通常我们会连接多个锁存器以便一次存储多个值,下面便是一个8位锁存器:

上面是8个数据输入端 D0-D7,下面是的8个输出端 Q7-Q0,当时钟信号为1时,D 端的信号将被输送到 Q 端,当时钟信号为0时,Q 端将保持上次Clk设为1时的状态。

边沿触发的 D 型触发器

上面的 D 型触发器对于简单的应用来说已经够了,不过他还存在一个问题,如果要使数据端的值保持在锁存器中,则必须将时钟信号设为1,但当时钟信号为1时,数据端的值是可能改变的,此时数据端的任何改变都会反应在触发器的输出中。

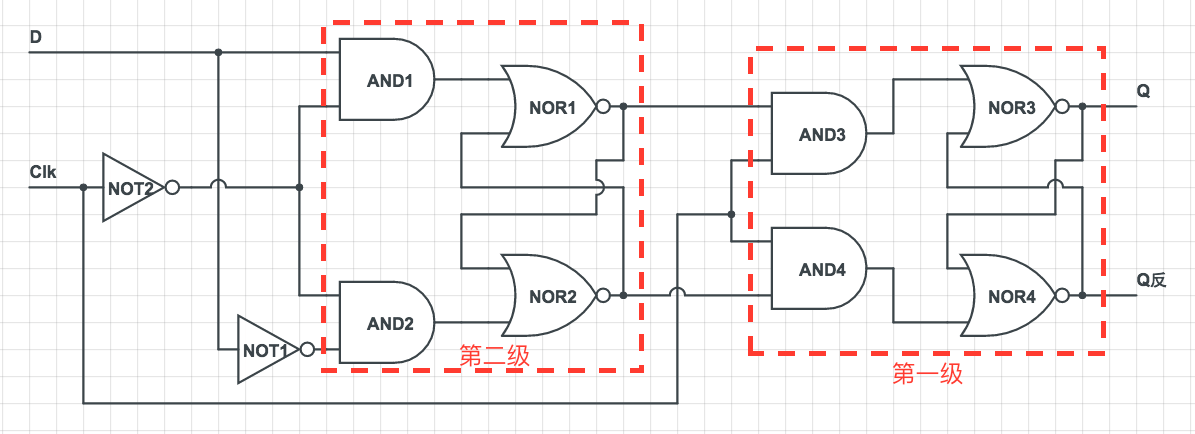

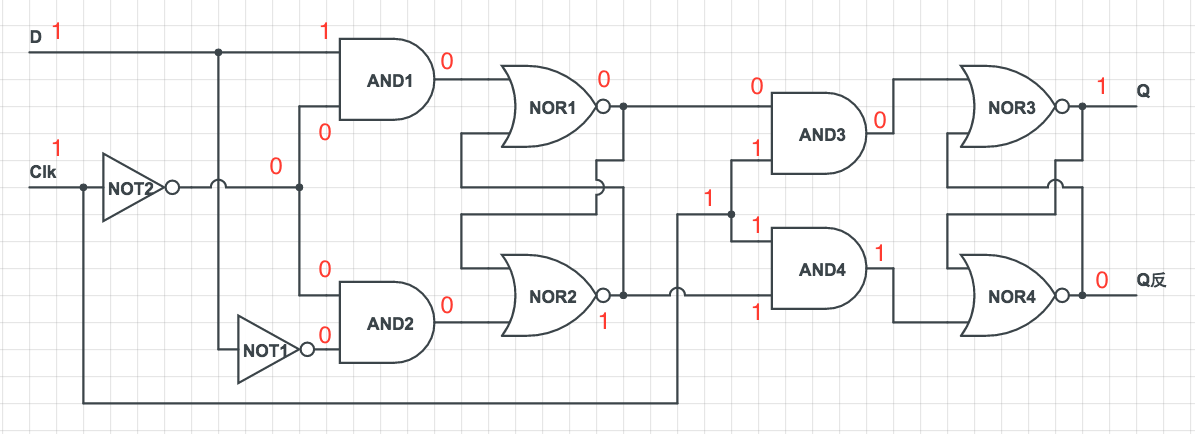

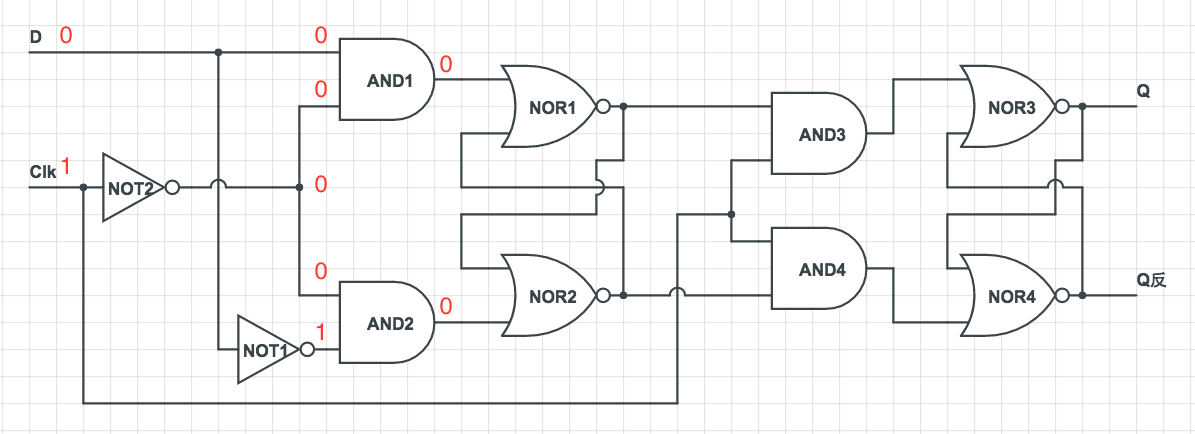

所以我们需要一种能更稳定的保持数据的触发器,这就是边沿触发的的 D 型触发器。它的特点是不论时钟信号是0还是1,数据端的输出都不会改变,而只有在时钟信号从0「跳变」到1的「瞬间」,数据端的输入才会反映到输出端。边沿触发的 D 型触发器与之前的 D 型触发器有些类似,它是由两个 D 型触发器结合而成的:

下面来分析一下它是如何工作的。

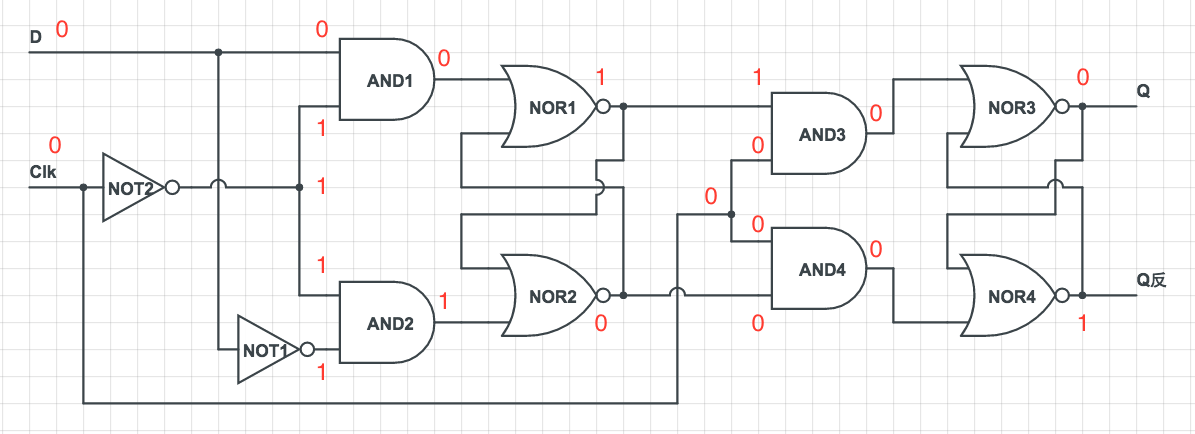

首先,触发器处于非工作状态,D 与 Clk 均为0,输出 Q 也为0:

接着使 D 为1,Clk 不变:

此时改变了第二级触发器的输出状态,但因为时钟信号仍为0,所以整体输出不变。

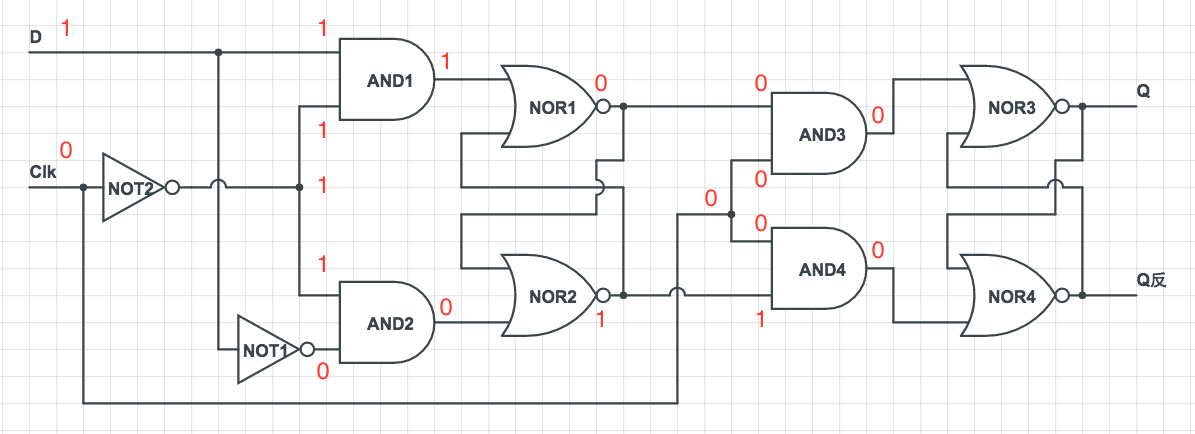

接着把 Clk 设为1:

因为 Clk 的跳变,第二级的输出并未变化,第一级使用了第二级的输出,并更新了整体电路的输出。

接着我们再将数据端变为0:

因为时钟为1,在第二级中输入的时钟信号其实是0,这就拦截住了数据端的任何变化。

上面就是边沿触发的 D 型触发器的几种输入状态了,通过下面的表格来总结下:

| 输入 | 输入 | 输出 | 输出 |

|---|---|---|---|

| D | Clk | Q | Q反 |

| 0 | ↑ | 0 | 1 |

| 1 | ↑ | 1 | 0 |

| X | 0 | Q | Q反 |

上面的 ↑ 表示时钟信号从0变为1时。

以上便是振荡器、触发器、锁存器的一些基本知识了。