随机访问存储器

上一篇中我们了解了「锁存器」,他能存储1位的二进制数,由此我们可以想到如果把大量的锁存器连接起来构成一个「锁存器阵列」,那不就可以存储大量数据了吗?事实确实如此,通过锁存器阵列构成的存储元件可以存储大量的 bit,我们称这个元件为「随机访问存储器」,也就是常说的「RAM」。现代 RAM 相比于最初的在结构与容量上都有着巨大的进步,但他们的使用原理仍是类似的。

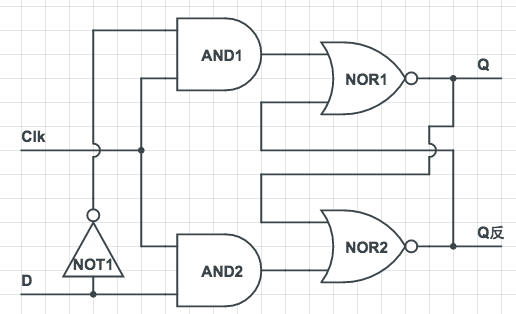

锁存器

前面我们说到了锁存器,现在来回顾一下它的结构:

这是一个电平触发的 D 型锁存器,它接收一个时钟信号,一个数据输入信号,一个数据输出信号(通常忽略Q),其中时钟信号用于控制锁存器是否存储数据。

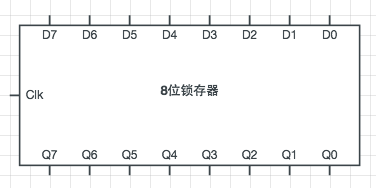

通过将多个锁存器连接在一次,我们获得了一次可以存储/读取 8 个 bit 的 8 位锁存器:

但是这样有一个问题,就是读写操作的粒度过大,一次操作的是一个字节,有时我们仅仅想存一个 bit,这样的结构就有些麻烦了,我们需要一种能够以更细粒度进行操作的存储结构。

数据读取

比一个字节更细的粒度就是一个bit 了,这也是二进制下信息的最小单位,所以我们希望能够指定某一 bit 来读取数据。当然,存储1 bit 的数据仍使用一个锁存器,要存储8个 bit 就要使用8个锁存器,但我们需要有一种选择方式来确定我们是从8个锁存器中的哪一个来读取数据。

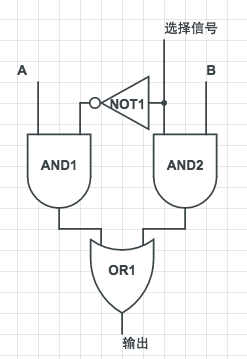

假设我们有一个开关(表示为0或1),0表示从左边的读取数据,1表示从右边读取数据,这个电路结构可以这样表示:

当选择信号为0,AND1其中输出为0或1,AND2输出恒为0,当两个与门输出同时输入或门,或门输出0或1 ,此时输出0或1是由AND1的数据输入端 A 决定。所以当选择信号为0时,整个电路选择了左边的数据输入,反之亦然。

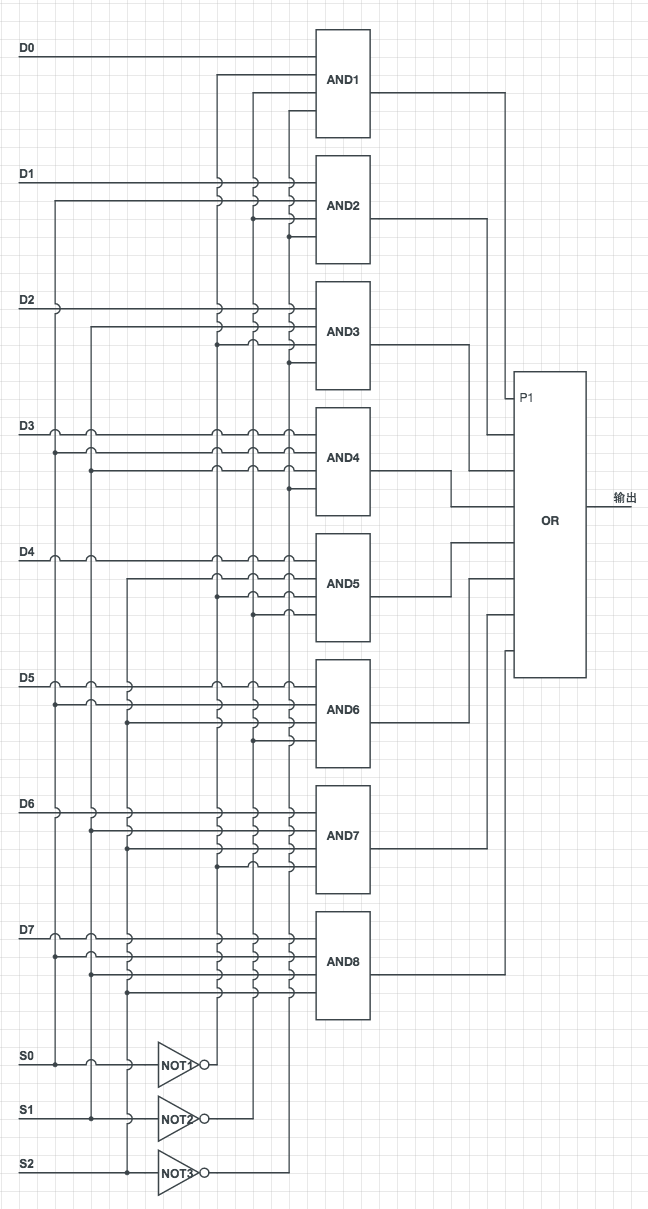

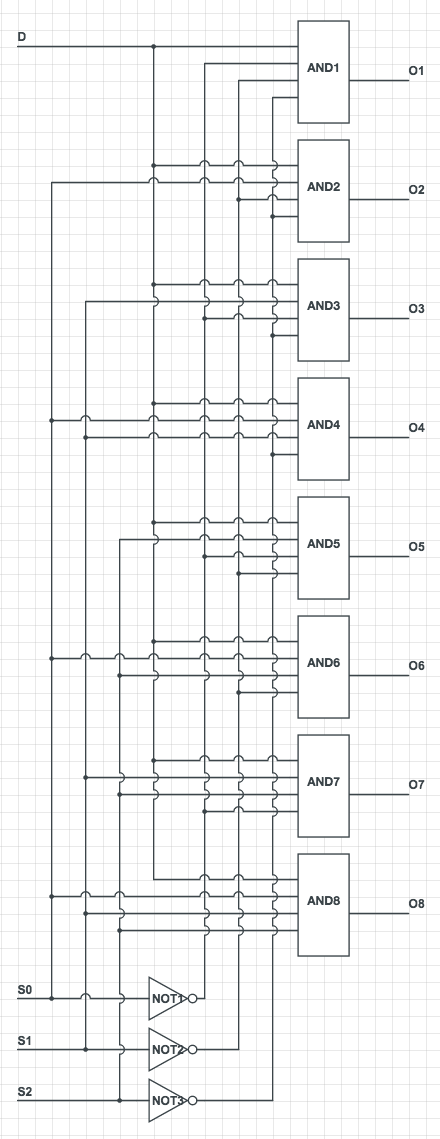

以上的结构称为「2-1选择器」,当选择开关增加到两个时,我们可以进行4选1,当增加到三个时,我们可以进行8选1。好了,现在我们就要使用「8-1选择器」来从8个锁存器中选一个来读取,下面就是8-1选择器的结构:

(因为画图软件不支持多输入门,所以与门和或门都画成了矩形)

(因为画图软件不支持多输入门,所以与门和或门都画成了矩形)

上图就是一个由2-1选择器拓展至的8-1选择器,S0-S2为三个开关,这三个开关的不同状态决定了唯一的数据输入。例如:当S0,S1,S2分别为110时,你会发现在8个与门中,只有 AND7 是除了数据输入端外所有控制端全为1的逻辑门,此时选择器整体的输出就由 AND7 的数据输入端决定。

如果你将每一个与门控制端全为1时的原始S0-S2信号进行计算,你会发现AND1-AND8被选中时其原始控制信号分别为:000, 001, 010, 011,100,101,110,111,刚好就跟3位二进制数的每一种情况顺序的对上了。

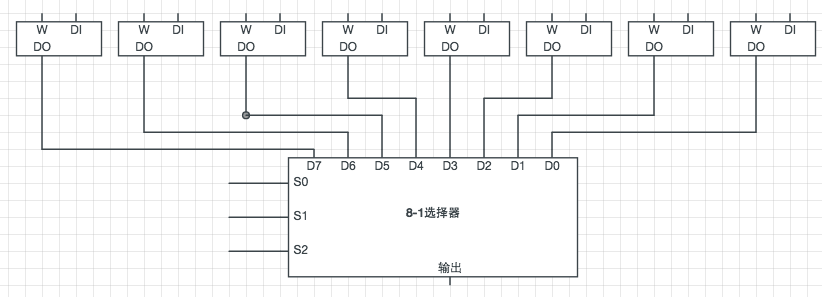

现在已经做好选择的准备了,接着我们把选择器与8个锁存器连接:

最上面一排是8个锁存器,W 为控制锁存器是否保存数据的信号,DI 为数据输入,DO 为数据输出,每个数据输出都连接到8-1选择器,通过控制端 S0-S2 的三个信号来决定从哪一个锁存器中读取数据。这里 S0-S2组成的三位二进制数也就是每一个锁存器的「地址」。

到此,存储器的随机读取已经搞定了。

数据写入

接着我们来搞数据的写入。同读取一样,写入也要能针对每一个锁存器进行单独的写入,所以数据写入部分的结构与数据读取差不多,不过有一点不同,在读取过程中需要有一个8-1的选择器来决定从哪一个锁存器来读取数据,而在写入过程中需要有一个元件来控制写入信号是要传递到8个锁存器中的哪一个,这个元件的结构与选择器类似,不过功能正好相反,这就是「3-8译码器」。

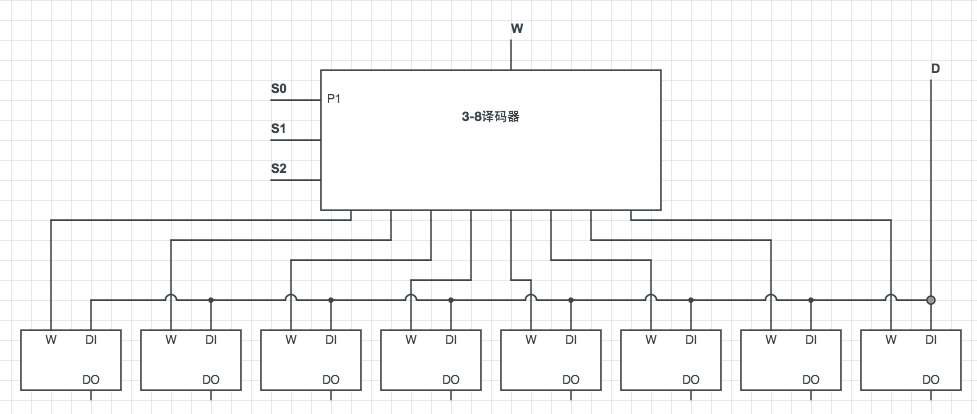

下面就是3-8译码器的结构:

(因为画图软件不支持多输入门,所以与门都画成了矩形)

(因为画图软件不支持多输入门,所以与门都画成了矩形)

D 代表输入信号,也就是写入控制信号,S0-S2来控制唯一选择的锁存器,O1-O8表示通过S0-S2选择为唯一一个输出。

接着我们把译码器与锁存器连接:

写入信号输入到3-8译码器中,通过 S0-S2 选择唯一的一个译码器并输入到其中,所有 DI 信号统一连接。

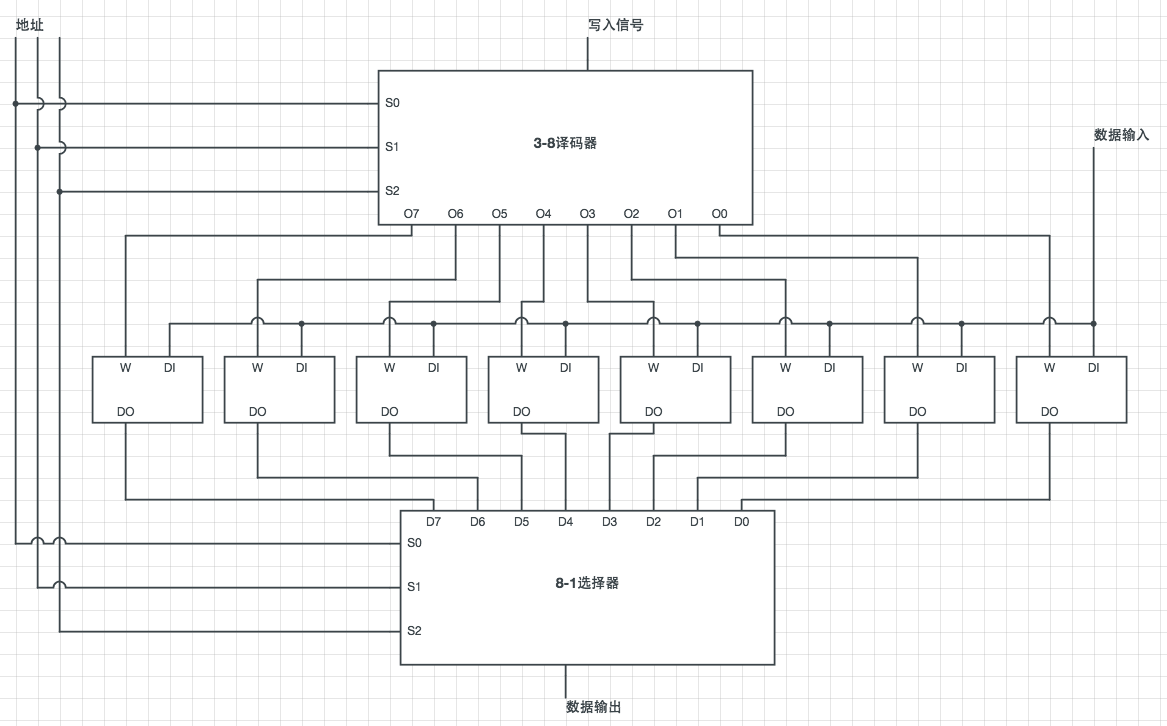

随机访问存储器

上面已经分别实现了数据的读写,接着我们需要把他们合并在一起,使这个系统变得可读写:

通过这样的结构,我们可以通过地址信号来找到唯一的一个锁存器来读写数据,这种结构也称为「随机访问存储器」,也就是常说的 RAM。上面的 RAM 可以存储8bit,也就是一个字节,通过将大量的 RAM 组合,我们可以搭建出可以存储大量数据的 RAM 阵列。